AAA (ASCII Adjust AL for Addition)

The aaa instruction is used to adjust the content of the AL register after that register has been used to perform the addition of two unpacked BCDs.

The algorithm is as follows

IF (al AND 0Fh > 9) or (AF = 1) ;; if low nibble of AL > 9 or the Auxilliary Flag is set

al = al+6

ah = ah+1

CF set

AF set

ENDIF

al = al AND 0Fh ;; clear the high nibble of AL

The auxiliary flag is set whenever there is an overflow of the lower 4 bits after an addition.

Example

mov al,7

add al,2 ;al = 9, AF clear, CF clear

aaa ;al = 9, ah is unchanged, CF clear

mov al,7

add al,6 ;al = 13 = 0Dh, al AND 0Fh = 0Dh > 9, AF clear, CF clear

aaa ;al = al+6 = 19 = 13h AND 0Fh = 3, ah=ah+1, CF set

mov al,7

add al,9 ;al = 16 = 10h, al AND 0Fh = 0 <= 9, AF set, CF clear

aaa ;al = al+6 = 22 = 16h AND 0Fh = 6, ah=ah+1, CF set

Because only the lower 4 bits of AL are retained, thus it is possible to add the ASCII values of numerical digits directly without the need to convert them to their binary values beforehand.

mov al,"7" ;37h

add al,"2" ;al = 37h+32h = 69h AND 0Fh = 9, AF clear, CF clear

aaa ;al = 69h AND 0Fh = 9, ah is unchanged, CF clear

Example of adding two large numbers

global _start

section .data

num1 db "491756380472816275825"

num2 db "8387562019932850157"

size1 dd 21

size2 dd 19

length db 0

section .bss

answer resb 32

section .text

_start:

; ECX will be used to hold the count of digits in the longer string

; EDX will be used to hold the count of digits in the shorter string

; ESI will be used to point to the current digit of the longer string

; EDI will be used to point to the current digit of the shorter string

; EBX will be used to point to the current digit of the answer

pushad

mov eax,[size1]

cmp eax,[size2]

jle .lower

mov ecx,[size1]

mov edx,[size2]

mov esi,num1

add esi,ecx ;points to the byte after the last digit

dec esi ;now points to last digit

mov edi,num2

add edi,edx ;points to the byte after the last digit

dec edi ;now points to last digit

jmp .init

.lower:

mov ecx,[size2]

mov edx,[size1]

mov esi,num2

add esi,ecx ;points to the byte after the last digit

dec esi ;now points to last digit

mov edi,num1

add edi,edx ;points to the byte after the last digit

dec edi ;now points to last digit

.init:

mov ebx,answer ; size for the answer and then load EBX with its address. the answer will be stored in reverse order

clc ;clear the CF before starting the addition

; The inc and dec instructions don't affect the CF.

; The CF would be affected if you change those for add reg,1 and sub reg,1

; and you would then need to save and restore that flag within the loops.

.shortloop:

mov al,[esi]

adc al,[edi] ;add the two digits and include CF from previous addition

aaa ;adjust the resulting digit of the addition

mov [ebx],al ;store it

inc ebx

dec esi

dec edi

dec ecx

dec edx

jnz .shortloop

; At this point, all the digits of the shorter number have been added.

; The remaining digits of the longer number must still be processed

; with any carry from previous additions.

inc ecx

dec ecx

jnz .longloop

jnc .finish ;no overflow from last addition

mov byte[ebx],1

inc ebx

jmp .finish

.longloop:

mov al,[esi]

adc al,0

aaa

mov [ebx],al

inc ebx

dec esi

dec ecx

jnz .longloop

jnc .finish ;no overflow from last addition

mov byte[ebx],1

inc ebx

.finish:

; At this point the answer is in reverse order and in binary format.

; The digits will now be reversed and converted to a null-terminated

; ASCII string ready for display.

; ESI will be used to point from the start of the answer

; EBX will be used to point from the end of the answer

; length will be used to count the length of the answer

mov byte[ebx],0 ;to terminate ASCII string

mov esi,answer

dec ebx ;point to last digit

.reverse:

inc byte[length] ;count the length of the answer

mov al,[esi]

mov ah,[ebx]

add ax,3030h ;convert both to ASCII

mov [esi],ah

mov [ebx],al

inc esi

dec ebx

cmp esi,ebx

jbe .reverse

popad ;restore all registers

mov eax,0x4

mov ebx,0x1

mov ecx,answer

mov edx,[length] ;the length of the answer

int 0x80 ;print the answer

; terminate

mov eax,0x1

xor ebx,ebx

int 0x80

| Instruction | Operands |

|---|---|

AAA |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

undefined. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

undefined. |

ZF |

undefined. |

AF |

sets to 1 if there is a decimal borrow; otherwise, it's cleared to 0. |

PF |

undefined. |

CF |

sets to 1 if there is a decimal borrow; otherwise, it's cleared to 0. |

AAD (ASCII Adjust AX before Division)

The aad is used to adjust the content of the AX register before that register is used to perform the division of two unpacked BCDs by another unpacked BCD digit.

The algorithm is as follows

AL = (AH * 10) + AL

AH = 0

Example

mov ax,0307h ; al = 07h, ah = 03h

aad ; al = (ah*10) + al, ah = 0

mov bl,5

div bl ; al = quotient, ah = remainder

| Instruction | Operands |

|---|---|

AAD |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

undefined. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result. |

ZF |

sets according to the result. |

AF |

undefined. |

PF |

sets according to the result. |

CF |

undefined. |

AAM (ASCII Adjust AX after Multiply)

The aam instruction is used to adjust the content of the AL and AH registers after the AL register has been used to perform the multiplication of two unpacked BCD bytes.

The algorithm is as follows

al = al mod 10

ah = al/10

Example

mov al,7

mov ah,3

mul ah ;al = 21 = 15h, ah = 0

aam ;al = 21 mod 10 = 1, ah = 21/10 = 2

In fact, this multiplication could be used without any preceding multiplication.

Example

mov al,73

aam ;al = 73 mod 10 = 3, ah = 73/10 = 7

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

undefined. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

undefined |

PF |

sets according to the result |

CF |

undefined |

ADC (Add with Carry)

The adc instruction is used to add the destination operand with source operand and also with the carry flag.

The algorithm is as follows

operand1 = operand1 + operand2 + CF

Example

STC ; set CF = 1

MOV AL, 5 ; AL = 5

ADC AL, 1 ; AL = AL + 1 + CF = 7

| Instruction | Operands |

|---|---|

ADC |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

sets according to the result. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result. |

ZF |

sets according to the result. |

AF |

sets according to the result. |

PF |

sets according to the result. |

CF |

sets according to the result. |

ADD (Add)

The adc instruction is used to add the destination operand with source operand.

The algorithm is as follows

operand1 = operand1 + operand2

Example

mov al, 5 ; al = 5

add al, -3 ; al = 2

| Instruction | Operands |

|---|---|

ADD |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

sets according to the result. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result. |

ZF |

sets according to the result. |

AF |

sets according to the result. |

PF |

sets according to the result. |

CF |

sets according to the result. |

AND (Logical AND)

The and instruction is used to perform a bitwise AND operation on the destination operand and source operand and stores the result in the destination operand.

The algorithm is as follows

operand1 = operand1 AND operand2

Example

mov al,'a' ; AL = 01100001b

and al,11011111b ; AL = 01000001b ('A')

| Instruction | Operands |

|---|---|

AND |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

cleared. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result. |

ZF |

sets according to the result. |

AF |

undefined. |

PF |

sets according to the result. |

CF |

cleared. |

CALL (Call Procedure)

The call instruction is used to save procedure linking information on the stack and branches to the procedure specified with the destination operand.

| Instruction | Operands |

|---|---|

CALL |

procedure name label |

CBW (Convert Byte to Word)

The cbw instruction is used to perform a bitwise AND operation on the destination operand and source operand and stores the result in the destination operand.

The algorithm is as follows

if high bit of AL = 1 then:

AH = 255 (0FFh)

else

AH = 0

Example

mov ax,0 ; AH = 0, AL = 0

mov al, -5 ; AX = 000FBh (251)

cbw ; AX = 0FFFBh (-5)

| Instruction | Operands |

|---|---|

CBW |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected. |

ZF |

unaffected. |

AF |

undefined. |

PF |

unaffected. |

CF |

unaffected. |

CDQ (Convert Double to Quad)

The cdq instruction is used to extend the sign bit of EAX into the EDX register.

The algorithm is as follows

if high bit of EAX = 1 then:

EDX = 0xFFFFFFFF

else

EDX = 0x0

Example

mov eax, 0x5 ; eax = 0x5, SF = 0

cdq ; edx = 0x00000000

mov eax, 0x5 ; eax = 0x5

neg eax ; eax = 0xFFFFFFFB, SF = 1

cdq ; edx = 0xFFFFFFFF

| Instruction | Operands |

|---|---|

CDQ |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected. |

ZF |

unaffected. |

AF |

undefined. |

PF |

unaffected. |

CF |

unaffected. |

CLC (Clear Carry Flag)

The cdq instruction is used to clear the CF flag.

The algorithm is as follows

CF = 0

| Instruction | Operands |

|---|---|

CLC |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected. |

ZF |

unaffected. |

AF |

undefined. |

PF |

unaffected. |

CF |

cleared to 0. |

CLI (Clear Interrupt Flag)

The cli instruction is used to clear the IF flag, interrupts disabled when interrupt flag cleared.

The algorithm is as follows

IF = 0

| Instruction | Operands |

|---|---|

CLI |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected. |

DF |

unaffected |

IF |

cleared to 0 |

TF |

unaffected |

SF |

unaffected. |

ZF |

unaffected. |

AF |

undefined. |

PF |

unaffected. |

CF |

unaffected. |

CMC (Complement Carry Flag)

The cmc instruction is used to invert the value of CF flag.

The algorithm is as follows

if CF = 1 then CF = 0

if CF = 0 then CF = 1

| Instruction | Operands |

|---|---|

CMC |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected. |

ZF |

unaffected. |

AF |

undefined. |

PF |

unaffected. |

CF |

contains the complement of its original value. |

CMP (Compare Two Operands)

The cmc instruction is used to compare the first operand with the second operand and sets the status flag in the EFLAGS register according to the results.

The algorithm is as follows

operand1 - operand2

Example

mov al, 5

mov bl, 5

cmp al, bl ; AL = 5, ZF = 1 (so equal!)

| Instruction | Operands |

|---|---|

CMP |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result. |

ZF |

sets according to the result. |

AF |

sets according to the result. |

PF |

sets according to the result. |

CF |

sets according to the result. |

CMPSB (Compare Two Operands)

The cmpsb instruction is used to compare the byte specified with the first operand with the byte specified with the second operand and sets the status flag in the EFLAGS register according to the results. The address of the first operand is read from the DS:SI registers. The address of the second operand is read from the ES:DI registers.

The algorithm is as follows

DS:[SI] - ES:[DI]

set flags according to result:

OF, SF, ZF, AF, PF, CF

if DF = 0 then

SI = SI + 1

DI = DI + 1

else

SI = SI - 1

DI = DI - 1

Example

cld ;Scan in the forward direction

mov cx, 100 ;Scanning 100 bytes (CX is used by REPE)

lea si, buffer1 ;Starting address of first buffer

lea di, buffer2 ;Starting address of second buffer

repe cmpsb ; ...and compare it.

jne mismatch ;The Zero Flag will be cleared if there is a mismatch

| Instruction | Operands |

|---|---|

CMPSB |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

sets according to the temporary result of the comparison. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the temporary result of the comparison. |

ZF |

sets according to the temporary result of the comparison. |

AF |

sets according to the temporary result of the comparison. |

PF |

sets according to the temporary result of the comparison. |

CF |

sets according to the temporary result of the comparison. |

CMPSW (Compare Two Operands)

The cmpsw instruction is used to compare the word specified with the first operand with the word specified with the second operand and sets the status flag in the EFLAGS register according to the results. The address of the first operand is read from the DS:SI registers. The address of the second operand is read from the ES:DI registers.

The algorithm is as follows

DS:[SI] - ES:[DI]

set flags according to result:

OF, SF, ZF, AF, PF, CF

if DF = 0 then

SI = SI + 2

DI = DI + 2

else

SI = SI - 2

DI = DI - 2

Example

; set forward direction:

cld

; load source into ds:si,

; load target into es:di:

mov ax, cs

mov ds, ax

mov es, ax

lea si, dat1

lea di, dat2

; set counter to data length in words:

mov cx, size

; compare until equal:

repe cmpsw

jnz not_equal

; "yes" - equal!

mov al, 'y'

mov ah, 0eh

int 10h

jmp exit_here

not_equal:

; "no" - not equal!

mov al, 'n'

mov ah, 0eh

int 10h

exit_here:

; wait for any key press:

mov ah, 0

int 16h

ret

; data vectors must have equal lengths:

x1:

dat1 dw 1234h, 5678h, 9012h, 3456h

dat2 dw 1234h, 5678h, 9012h, 3456h

size = ($ - x1) / 4

| Instruction | Operands |

|---|---|

CMPSW |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

sets according to the temporary result of the comparison. |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the temporary result of the comparison. |

ZF |

sets according to the temporary result of the comparison. |

AF |

sets according to the temporary result of the comparison. |

PF |

sets according to the temporary result of the comparison. |

CF |

sets according to the temporary result of the comparison. |

CWD (Convert Word To Doubleword)

The cwd instruction is used to extend the sign bit of AX into the DX register.

The algorithm is as follows

if high bit of AX = 1 then:

DX = 65535 (0FFFFh)

else

DX = 0

Example

mov dx, 0 ; DX = 0

mov ax, 0 ; AX = 0

mov ax, -5 ; DX:AX = 00000h:0FFFBh

cwd ; DX:AX = 0FFFFh:0FFFBh

| Instruction | Operands |

|---|---|

CWD |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

DAA (Decimal Adjust AL after Addition)

The cwd instruction is used to adjust the content of the AL register after that register is used to perform the addition of two packed BCDs.

The algorithm is as follows

IF (al AND 0Fh > 9) or (the Auxilliary Flag is set)

al = al+6

AF set

ENDIF

IF (al > 99h) or (Carry Flag is set)

al = al + 60h

CF set

ENDIF

Example

mov dx, 0 ; DX = 0

mov ax, 0 ; AX = 0

mov ax, -5 ; DX:AX = 00000h:0FFFBh

cwd ; DX:AX = 0FFFFh:0FFFBh

| Instruction | Operands |

|---|---|

DAA |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

sets if the adjustment of the value results in a decimal carry in either digit of the result |

PF |

sets according to the result |

CF |

sets if the adjustment of the value results in a decimal carry in either digit of the result |

DAS (Decimal Adjust AL after Subtraction)

The das instruction is used to adjust the content of the AL register after that register is used to perform the subtraction of two packed BCDs.

The algorithm is as follows

if low nibble of AL > 9 or AF = 1 then:

AL = AL - 6

AF = 1

if AL > 9Fh or CF = 1 then:

AL = AL - 60h

CF = 1

Example

mov dx, 0 ; DX = 0

mov ax, 0 ; AX = 0

mov ax, -5 ; DX:AX = 00000h:0FFFBh

cwd ; DX:AX = 0FFFFh:0FFFBh

| Instruction | Operands |

|---|---|

DAS |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

sets if the adjustment of the value results in a decimal carry in either digit of the result |

PF |

sets according to the result |

CF |

sets if the adjustment of the value results in a decimal carry in either digit of the result |

DEC (Decrement)

The dec instruction is used to subtract 1 from the destination operand while preserving the state of the CF flag.

The algorithm is as follows

operand = operand - 1

Example

mov al, 255 ; AL = 0FFh (255 or -1)

dec al ; AL = 0FEh (254 or -2)

| Instruction | Operands |

|---|---|

DEC |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

sets according to the result |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

sets according to the result |

PF |

sets according to the result |

CF |

unaffected |

DIV (Unsigned Divide)

The div instruction is used to divide (unsigned) the value in the AX register, DX:AX register pair or EDX:EAX register pair (dividend) by the source operand (divisor) and stores the result in the AX.

The algorithm is as follows

when operand is a byte:

AL = AX / operand

AH = remainder (modulus)

when operand is a word:

AX = (DX AX) / operand

DX = remainder (modulus)

Example

mov ax, 203 ; AX = 00CBh

mov bl, 4

div bl ; AL = 50 (32h), AH = 3

| Instruction | Operands |

|---|---|

DIV |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

HLT (Halt)

The hlt instruction is used to stop instruction execution and place the processor in the HALT state.

Example

mov eax, 5

hlt

| Instruction | Operands |

|---|---|

HLT |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

IDIV (Signed Divide)

The idiv instruction is used to divide (signed) the value in the AL, AX, or EAX register by the source operand and store the result in the AX, DX:AX, or EDX:EAX registers.

The algorithm is as follows

when operand is a byte:

AL = AX / operand

AH = remainder (modulus)

when operand is a word:

AX = (DX AX) / operand

DX = remainder (modulus)

Example

mov ax, -203 ; AX = 0FF35h

mov bl, 4

idiv bl ; AL = -50 (0CEh), AH = -3 (0FDh)

| Instruction | Operands |

|---|---|

IDIV |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

IMUL (Signed Multiply)

The imul instruction is used to multiply AL, AX, or EAX registers (depending on the operand size) with the source operand and store the product in the AX, DX:AX, or EDX:EAX registers.

The algorithm is as follows

when operand is a byte:

AX = AL * operand

when operand is a word:

(DX AX) = AX * operand

Example

mov al, -2

mov bl, -4

imul bl ; AX = 8

| Instruction | Operands |

|---|---|

IDIV |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

For the one operand form of the instruction, sets when significant bits are carried into the upper half of the result and cleared when the result fits exactly in the lower half of the result. For the two- and three-operand forms of the instruction, sets when the result must be truncated to fit in the destination operand size and cleared when the result fits exactly in the destination operand size |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

For the one operand form of the instruction, sets when significant bits are carried into the upper half of the result and cleared when the result fits exactly in the lower half of the result. For the two- and three-operand forms of the instruction, sets when the result must be truncated to fit in the destination operand size and cleared when the result fits exactly in the destination operand size |

INC (Increment)

The inc instruction is used to add 1 from the destination operand while preserving the state of the CF flag.

The algorithm is as follows

operand = operand + 1

Example

mov al, 4

inc al ; AL = 5

| Instruction | Operands |

|---|---|

INC |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

sets according to the result |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

sets according to the result |

PF |

sets according to the result |

CF |

unaffected |

INT (Interrupt)

The inc instruction is used to generate a call to the interrupt or except handler specified with the destination operand. The destination operand specifies an interrupt vector number from 0 to 255, encoded as 8-bit unsigned intermediate value. Each interrupt vector number provides index to a gate descriptor in the IDT. The interrupt vector number specifies an interrupt descriptor in the interrupt descriptor table (IDT). It provides index into the IDT. The selected interrupt descriptor in turn contains a pointer to an interrupt or exception handler procedure. In protected mode, the IDT contains an array of 8-byte descriptors, each of which is an interrupt gate, trap gate or task gate. In real-address mode, the IDT is an array of 4-byte far pointers (2-byte code segment selector and a 2-byte instruction pointer), each of which point directly to a procedure in the selected segment. (In real-address mode, the IDT is called the interrupt vector table, and its pointers are called interrupt vectors).

The algorithm is as follows

Push to stack:

- flags register

- CS

- IP

IF = 0

Transfer control to interrupt procedure

Example

mov ah, 0eh ; teletype

mov al, 'A'

int 10h ; BIOS interrupt

| Instruction | Operands |

|---|---|

INT |

immediate byte |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

VM |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

RF |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

NT |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

IOPL |

unaffected |

OF |

sets according to the result |

DF |

unaffected |

IF |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

TF |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

sets according to the result |

PF |

sets according to the result |

CF |

unaffected |

INTO (Call to Interrupt Procedure)

The into instruction is used to call interrupt 4 if overflow flag is 1.

The algorithm is as follows

if OF = 1 then INT 4

Example

; -5 - 127 = -132 (not in -128..127)

; the result of SUB is wrong (124),

; so OF = 1 is set:

mov al, -5

sub al, 127 ; AL = 7Ch (124)

into ; process error.

| Instruction | Operands |

|---|---|

INTO |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

VM |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

RF |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

NT |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

IOPL |

unaffected |

OF |

sets according to the result |

DF |

unaffected |

IF |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

TF |

may be cleared, depending on the mode of operation of the processor when the INT instruction is executed |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

sets according to the result |

PF |

sets according to the result |

CF |

unaffected |

IRET (Interrupt Return)

The iret instruction is used to return program control from an exception or interrupt handler to a program or procedure that was interrupted by an exception, an external interrupt, or a software-generated interrupt.

The algorithm is as follows

Pop from stack:

- IP

- CS

- flags register

| Instruction | Operands |

|---|---|

IRET |

no operands |

| Flags | |

|---|---|

ID |

affected |

VIP |

affected |

VIF |

affected |

AC |

affected |

VM |

affected |

RF |

affected |

NT |

affected |

IOPL |

affected |

OF |

affected |

DF |

affected |

IF |

affected |

TF |

affected |

SF |

affected |

ZF |

affected |

AF |

affected |

PF |

affected |

CF |

affected |

Jump Instructions

| Instruction | Operands | Meaning | Jump Condition |

|---|---|---|---|

JA |

label | Jump if Above | CF=0 and ZF=0 |

JAE |

label | Jump if Above or Equal | CF=0 |

JB |

label | Jump if Below | CF=1 |

JBE |

label | Jump if Below or Equal | CF=1 or ZF=1 |

JC |

label | Jump if Carry | CF=1 |

JCXZ |

label | Jump if CX Zero | CX=0 |

JE |

label | Jump if Equal | ZF=1 |

JG |

label | Jump if Greater (signed) | ZF=0 and SF=OF |

JGE |

label | Jump if Greater or Equal (signed) | SF=OF |

JL |

label | Jump if Less (signed) | SF != OF |

JLE |

label | Jump if Less or Equal (signed) | ZF=1 or SF != OF |

JMP |

label | Unconditional Jump | unconditional |

JNA |

label | Jump if Not Above | CF=1 or ZF=1 |

JNAE |

label | Jump if Not Above or Equal | CF=1 |

JNB |

label | Jump if Not Below | CF=0 |

JNBE |

label | Jump if Not Below or Equal | CF=0 and ZF=0 |

JNC |

label | Jump if Not Carry | CF=0 |

JNE |

label | Jump if Not Equal | ZF=0 |

JNG |

label | Jump if Not Greater (signed) | ZF=1 or SF != OF |

JNGE |

label | Jump if Not Greater or Equal (signed) | SF != OF |

JNL |

label | Jump if Not Less (signed) | SF=OF |

JNLE |

label | Jump if Not Less or Equal (signed) | ZF=0 and SF=OF |

JNO |

label | Jump if Not Overflow (signed) | OF=0 |

JNP |

label | Jump if No Parity | PF=0 |

JNS |

label | Jump if Not Signed (signed) | SF=0 |

JNZ |

label | Jump if Not Zero | ZF=0 |

JO |

label | Jump if Overflow (signed) | OF=1 |

JP |

label | Jump if Parity | PF=1 |

JPE |

label | Jump if Parity Even | PF=1 |

JPO |

label | Jump if Parity Odd | PF=0 |

JS |

label | Jump if Signed (signed) | SF=1 |

JZ |

label | Jump if Zero | ZF=1 |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LAHF (Load Status Flags into AH Register)

The lahf instruction is used to move the low byte of the EFLAGS register (which includes status flags SF, ZF, AF, PF, and CF) to the AH register.

The algorithm is as follows

AH = flags register

| Instruction | Operands |

|---|---|

LAHF |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LEA (Load Effective Address)

The lea instruction is used to compute the effective address of the second operand and store it in the

first operand.

The algorithm is as follows

REG = address of memory (offset)

Example

mov bx, 35h

mov di, 12h

lea si, [bx+di] ; SI = 35h + 12h = 47h

| Instruction | Operands |

|---|---|

LEA |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LODSB

The lodsb instruction is used to load a byte from the source operand into the AL register. The source operand is a memory location, the address of which is read from the DS:SI register. If the DF flag is 1, the SI register is decremented. The SI register is incremented or decremented by 1.

The algorithm is as follows

AL = DS:[SI]

if DF = 0 then

SI = SI + 1

else

SI = SI - 1

Example

section .text

global _start ;must be declared for using gcc

_start: ;tell linker entry point

mov ecx, len

mov esi, s1

mov edi, s2

loop_here:

lodsb

add al, 02

stosb

loop loop_here

cld

rep movsb

mov edx,20 ;message length

mov ecx,s2 ;message to write

mov ebx,1 ;file descriptor (stdout)

mov eax,4 ;system call number (sys_write)

int 0x80 ;call kernel

mov eax,1 ;system call number (sys_exit)

int 0x80 ;call kernel

section .data

s1 db 'password', 0 ;source

len equ $-s1

section .bss

s2 resb 10 ;destination

| Instruction | Operands |

|---|---|

lodsb |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LODSW

The lodsw instruction is used to load a word from the source operand into the AX register. The source operand is a memory location, the address of which is read from the DS:SI register. If the DF flag is 1, the SI register is decremented. The SI register is incremented or decremented by 2.

The algorithm is as follows

AX = DS:[SI]

if DF = 0 then

SI = SI + 2

else

SI = SI - 2

| Instruction | Operands |

|---|---|

lodsw |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LODSD

The lodsd instruction is used to load a double word from the source operand into the EAX register. The source operand is a memory location, the address of which is read from the DS:ESI register. If the DF flag is 1, the ESI register is decremented. The ESI register is incremented or decremented by 4.

The algorithm is as follows

AX = DS:[ESI]

if DF = 0 then

ESI = ESI + 4

else

ESI = ESI - 4

| Instruction | Operands |

|---|---|

lodsd |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LOOP

The loop instruction is used to perform a loop operation using the ECX or CX register as a counter. Each

time the loop instruction is executed, the count register is decremented, then checked for 0. If the count is 0, the

loop is terminated and program execution continues with the instruction following the LOOP instruction. If the count is

not zero, a near jump is performed to the destination operand.

The algorithm is as follows

CX = CX - 1

if CX <> 0 then

jump

else

no jump, continue

Example

section .text

global _start ;must be declared for using gcc

_start: ;tell linker entry point

mov ecx,10

mov eax, '1'

l1:

mov [num], eax

mov eax, 4

mov ebx, 1

push ecx

mov ecx, num

mov edx, 1

int 0x80

mov eax, [num]

sub eax, '0'

inc eax

add eax, '0'

pop ecx

loop l1

mov eax,1 ;system call number (sys_exit)

int 0x80 ;call kernel

section .bss

num resb 1

| Instruction | Operands |

|---|---|

loop |

label |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LOOPE / LOOPZ

The loope instruction is used to perform a loop operation using the ECX or CX register as a counter. Each

time the loop instruction is executed, the count register is decremented. If the count is 0, the loop is terminated and program execution continues with the instruction following the LOOPE instruction. If the count is not and ZF flag is set to 1, a near jump is performed to the destination operand.

The algorithm is as follows

CX = CX - 1

if CX <> 0 and (ZF = 1) then

jump

else

no jump, continue

| Instruction | Operands |

|---|---|

loope / loopz |

label |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

LOOPNE / LOOPNZ

The loopne instruction is used to perform a loop operation using the ECX or CX register as a counter. Each

time the loop instruction is executed, the count register is decremented, then checked for 0. If the count is 0,

the loop is terminated and program execution continues with the instruction following the LOOPNE instruction. If the

count is not and ZF flag is set to 0, a near jump is performed to the destination operand.

The algorithm is as follows

CX = CX - 1

if CX <> 0 and (ZF = 0) then

jump

else

no jump, continue

| Instruction | Operands |

|---|---|

loopne / loopnz |

label |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

MOV

The mov instruction is used to copy the second operand to the first operand.

The algorithm is as follows

operand1 = operand2

| Instruction | Operands |

|---|---|

mov |

REG, memory REG, REG memory, immediate REG, immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

MOVSB

The movsb instruction is used to move a byte at DS:SI to ES:DI. After the move operation, the SI and DI registers are incremented or decremented automatically according to the setting of the DF flag. The SI and DI registers are incremented or decremented by 1 byte.

The algorithm is as follows

ES:[DI] = DS:[SI]

if DF = 0 then

SI = SI + 1

DI = DI + 1

else

SI = SI - 1

DI = DI - 1

section .text

global _start ;must be declared for using gcc

_start: ;tell linker entry point

mov ecx, len

mov esi, s1

mov edi, s2

cld

rep movsb

mov edx,20 ;message length

mov ecx,s2 ;message to write

mov ebx,1 ;file descriptor (stdout)

mov eax,4 ;system call number (sys_write)

int 0x80 ;call kernel

mov eax,1 ;system call number (sys_exit)

int 0x80 ;call kernel

section .data

s1 db 'Hello, world!',0 ;string 1

len equ $-s1

section .bss

s2 resb 20 ;destination

| Instruction | Operands |

|---|---|

movsb |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

MOVSW

The movsw instruction is used to move a word at DS:SI to ES:DI. After the move operation, the SI and DI registers are incremented or decremented automatically according to the setting of the DF flag. The SI and DI registers are incremented or decremented by 2 byte.

The algorithm is as follows

ES:[DI] = DS:[SI]

if DF = 0 then

SI = SI + 2

DI = DI + 2

else

SI = SI - 2

DI = DI - 2

| Instruction | Operands |

|---|---|

movsw |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

MOVSD

The movsd instruction is used to move a double word at DS:ESI to ES:EDI. After the move operation, the SI and DI registers are incremented or decremented automatically according to the setting of the DF flag. The SI and DI registers are incremented or decremented by 4 byte.

The algorithm is as follows

ES:[DI] = DS:[SI]

if DF = 0 then

SI = SI + 4

DI = DI + 4

else

SI = SI - 4

DI = DI - 4

| Instruction | Operands |

|---|---|

movsd |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

MOVSX

The movsx instruction is used to copy the content of the source operand to the destination operand and sign

extends the value to 16 or 32 bits with 1. The size of the converted value depends on the operand-size attribute.

Example

mov bx, 0C3EEh ; Sign bit of bl is now 1: BH == 1100 0011, BL == 1110 1110

movsx ebx, bx ; Load signed 16-bit value into 32-bit register and sign-extend

; EBX is now equal FFFFC3EEh

| Instruction | Operands |

|---|---|

movsx |

REG, REG REG, memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

MUL (Unsigned Multiply)

The mul instruction is used to perform an unsigned multiplication of the first operand (AL, AX, or EAX) and

the second operand and stores the result in the destination operand (AX, DX:AX, or EDX:EAX).

The algorithm is as follows

when operand is a byte:

ax = al * operand

when operand is a word:

(dx:ax) = ax * operand

| Instruction | Operands |

|---|---|

mul |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

cleared to 0 if the upper half of the result is 0; otherwise, they are set to 1 |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

cleared to 0 if the upper half of the result is 0; otherwise, they are set to 1 |

NEG

The neg instruction is used to replace the value of the operand with its two’s complement.

The algorithm is as follows

Invert all bits of the operand

Add 1 to inverted operand

mov al, 5 ; AL = 05h

neg al ; AL = 0FBh (-5)

neg al ; AL = 05h (5)

| Instruction | Operands |

|---|---|

neg |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

sets according to the result |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

sets according to the result |

PF |

sets according to the result |

CF |

cleared to 0 if the upper half of the result is 0; otherwise, they are set to 1 |

NOP

The nop instruction is used to perform no operation.

; do nothing, 3 times:

nop

nop

nop

ret

| Instruction | Operands |

|---|---|

nop |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

NOT

The not instruction is used to perform a bitwise NOT operation (each 1 is cleared to 0, and each 0 is set to 1) on the destination operand and stores the result in the destination operand location.

The algorithm is as follows

if bit is 1 turn it to 0

if bit is 0 turn it to 1

Example

mov al, 00011011b

not al ; AL = 11100100b

| Instruction | Operands |

|---|---|

not |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

OR (Logical Inclusive OR)

The or instruction is used to perform a bitwise OR operation between the destination and source operands and stores the result in the destination operand location.

Example

mov al, 'A' ; AL = 01000001b

or al, 00100000b ; AL = 01100001b ('a')

| Instruction | Operands |

|---|---|

or |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

cleared |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

sets according to the result |

ZF |

sets according to the result |

AF |

unaffected |

PF |

sets according to the result |

CF |

unaffected |

POP

The pop instruction is used to load the value from the top of the stack to the location specified with the destination operand and then increments the stack pointer. The address-size attribute of the stack segment determines the stack

pointer size (16 bits or 32 bits) and the operand-size attribute of the current code segment determines the amount of

the stack pointer is incremented (2 bytes or 4 bytes).

The algorithm is as follows

operand = SS:[SP] (top of the stack)

SP = SP + 2

Example

mov ax, 1234h

push ax

pop dx ; DX = 1234h

| Instruction | Operands |

|---|---|

or |

REG memory |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

cleared |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

POPA

The popa instruction is used to pop all general purpose registers DI, SI, BP, SP, BX, DX, CX, AX from the stack. SP value is ignored, it is popped but not set to SP register

| Instruction | Operands |

|---|---|

popa |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

POPAD

The popa instruction is used to pop all general purpose registers edi, esi, ebp, esp, ebx, edx, ecx, eax from the stack. ESP value is ignored, it is popped but not set to ESP register

| Instruction | Operands |

|---|---|

popad |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

POPF

The popf instruction is used to get flags register stored in the stack.

The algorithm is as follows

flags = SS:[SP] (top of the stack)

SP = SP + 2

| Instruction | Operands |

|---|---|

popf |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

POPFD

The popfd instruction is used to get flags register stored in the stack.

The algorithm is as follows

flags = SS:[ESP] (top of the stack)

ESP = ESP + 2

| Instruction | Operands |

|---|---|

popfd |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

PUSH

The push instruction is used to store the value of the destination operand into the stack and decrements the stack pointer.

The algorithm is as follows

SP = SP - 2

SS:[SP] (top of the stack) = operand

Example

mov ax, 1234h

push ax

pop dx ; DX = 1234h

| Instruction | Operands |

|---|---|

push |

REG memory immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

PUSHA

The pusha instruction is used to push all general purpose registers AX, CX, DX, BX, SP, BP, SI, DI into the

stack.

| Instruction | Operands |

|---|---|

pusha |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

PUSHAD

The pushad instruction is used to push all general purpose registers eax, ecx, edx, ebx, esp, ebp, esi, edi

into the stack.

| Instruction | Operands |

|---|---|

pushad |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

PUSHF

The pushf instruction is used to store flags register in the stack.

The algorithm is as follows

SP = SP - 2

SS:[SP] (top of the stack) = flags

| Instruction | Operands |

|---|---|

pushf |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

PUSHFD

The pushfd instruction is used to store flags register in the stack.

The algorithm is as follows

ESP = ESP - 2

SS:[ESP] (top of the stack) = flags

| Instruction | Operands |

|---|---|

pushfd |

no operands |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

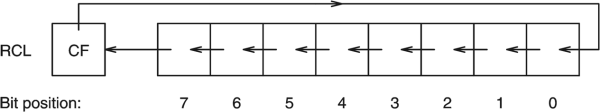

RCL

The rcl instruction is used to shift (rotate) the bits of the first operand, the number of bit positions specified in the second operand and stores the result in the destination operand. The RCL instruction shifts the CF flag into the least-significant bit and shifts the most significant bit into the CF flag.

The algorithm is as follows

shift all bits left, the bit that goes off is set to CF and previous value of CF is inserted to the right-most position.

Example

stc ; set carry (CF=1).

mov al, 1ch ; AL = 00011100b

rcl al, 1 ; AL = 00111001b, CF=0

| Instruction | Operands |

|---|---|

rcl |

memory, immediate REG, immediate memory, CL REG, CL |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

affected only for single-bit rotates. It is undefined for multi-bit rotates |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

contains the value of the bit shifted into it |

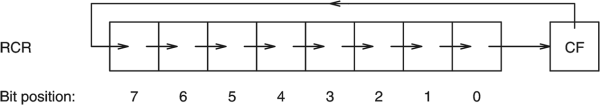

RCR

The rcr instruction is used to shift (rotate) the bits of the first operand, the number of bit positions specified in the second operand and stores the result in the destination operand. The RCR instruction shifts the CF flag into the most-significant bit and shifts the less-significant bit into the CF flag.

The algorithm is as follows

shift all bits right, the bit that goes off is set to CF and previous value of CF is inserted to the leftmost position.

Example

stc ; set carry (CF=1)

mov al, 1ch ; AL = 00011100b

rcr al, 1 ; AL = 10001110b, CF=0

| Instruction | Operands |

|---|---|

rcr |

memory, immediate REG, immediate memory, CL REG, CL |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

affected only for single-bit rotates it is undefined for multi-bit rotates |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

contains the value of the bit shifted into it |

REP (Repeat)

The rep instruction is used to repeat following movsb, movsw, movsd, lodsb, lodsw, lodsd, stosb, stosw, stosd instructions (E)CX times.

The algorithm is as follows

check_cx:

if CX <> 0 then

do following chain instruction

CX = CX - 1

go back to check_cx

else

exit from REP cycle

| Instruction | Operands |

|---|---|

rep |

chain instructions |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

REPE / REPZ

The repe instruction is used to repeat following cpmsb, cpmsw, cpmsd, scasb, scasw, scasd while ZF = 1 (result is equal), maximum (E)CX times.

The algorithm is as follows

check_cx:

if CX <> 0 then

do following chain instruction

CX = CX - 1

if ZF = 1 then:

go back to check_cx

else

exit from REPE cycle

else

exit from REPE cycle

| Instruction | Operands |

|---|---|

repe |

chain instructions |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

REPNE / REPNZ

The repne instruction is used to repeat following cpmsb, cpmsw, cpmsd, scasb, scasw, scasd while ZF = 0 (result is not equal), maximum (E)CX times.

The algorithm is as follows

check_cx:

if CX <> 0 then

do following chain instruction

CX = CX - 1

if ZF = 0 then:

go back to check_cx

else

exit from REPNE cycle

else

exit from REPNE cycle

| Instruction | Operands |

|---|---|

repne |

chain instructions |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

RET

The ret instruction is used to return program control to a return address located on the top of the stack. The address is usually placed on the stack by call instruction.

The algorithm is as follows

Pop from stack:

IP

CS

if immediate operand is present:

SP = SP + operand

| Instruction | Operands |

|---|---|

ret |

no operands or even immediate |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

unaffected |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

unaffected |

ROL

The rol instruction is used to shift all the bits toward more significant bit positions except for the most-significant bit, which is rotated to the least-significant bit location.

Example

mov al, 1ch ; AL = 00011100b

rol al, 1 ; AL = 00111000b, CF=0

| Instruction | Operands |

|---|---|

rol |

memory, immediate REG, immediate memory, CL REG, CL |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

affected only for single-bit rotates; it is undefined for multi-bit rotates |

DF |

unaffected |

IF |

unaffected |

TF |

unaffected |

SF |

unaffected |

ZF |

unaffected |

AF |

unaffected |

PF |

unaffected |

CF |

contains the value of the bit shifted into it |

ROR

The ror instruction is used to shift all the bits toward least significant bit positions except for the least-significant bit, which is rotated to the most-significant bit location.

Example

mov al, 1ch ; AL = 00011100b

ror al, 1 ; AL = 00001110b, CF=0

| Instruction | Operands |

|---|---|

ror |

memory, immediate REG, immediate memory, CL REG, CL |

| Flags | |

|---|---|

ID |

unaffected |

VIP |

unaffected |

VIF |

unaffected |

AC |

unaffected |

VM |

unaffected |

RF |

unaffected |

NT |

unaffected |

IOPL |

unaffected |

OF |

affected only for single-bit rotates; it is undefined for multi-bit rotates |

DF |

unaffected |

IF |